In electronics, an adder or summer is a digital circuit that performs addition of numbers. In modern computers adders reside in thearithmetic logic unit (ALU) where other operations are performed. Although adders can be constructed for many numerical representations, such as Binary-coded decimal or excess-3, the most common adders operate on binary numbers. In cases where two's complement or one's complement is being used to represent negative numbers, it is trivial to modify an adder into an adder-subtracter. Other signed number representations require a more complex adder.

Types

Half adder

A half adder is a logical circuit that performs an addition operation on two one-bit binary numbers often written as A and B. The half adder output is a sum of the two inputs usually represented with the signals Cout and S where  . Following is the logic table for a half adder:

. Following is the logic table for a half adder:

Inputs | Outputs | ||

|---|---|---|---|

A | B | C | S |

0 | 0 | 0 | 0 |

0 | 1 | 0 | 1 |

1 | 0 | 0 | 1 |

1 | 1 | 1 | 0 |

As an example, a Half Adder can be built with an XOR gate and an AND gate.

___________

A ------| |

| Half |-----  | Adder |

| |-----

| Adder |

| |-----  B ------|___________|

B ------|___________|

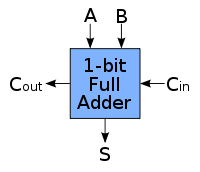

Full adder

A full adder is a logical circuit that performs an addition operation on three one-bit binary numbers often written as A, B, and Cin. The full adder produces a two-bit output sum typically represented with the signals Cout and S where  . The full adder's truth table is:

. The full adder's truth table is:

Inputs | Outputs | |||

|---|---|---|---|---|

A | B | Ci | Co | S |

0 | 0 | 0 | 0 | 0 |

1 | 0 | 0 | 0 | 1 |

0 | 1 | 0 | 0 | 1 |

1 | 1 | 0 | 1 | 0 |

0 | 0 | 1 | 0 | 1 |

1 | 0 | 1 | 1 | 0 |

0 | 1 | 1 | 1 | 0 |

1 | 1 | 1 | 1 | 1 |

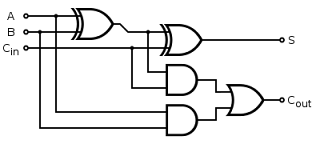

A full adder can be implemented in many different ways such as with a custom transistor-level circuit or composed of other gates. One example implementation is with  and

and  .

.

In this implementation, the final OR gate before the carry-out output may be replaced by an XOR gate without altering the resulting logic. Using only two types of gates is convenient if the circuit is being implemented using simple IC chips which contain only one gate type per chip.

A full adder can be constructed from two half adders by connectingA and B to the input of one half adder, connecting the sum from that to an input to the second adder, connecting Ci to the other input and OR the two carry outputs. Equivalently, S could be made the three-bit XOR of A, B, and Ci, and Co could be made the three-bit majority function of A, B, and Ci.

Multiple-bit adder

Ripple carry adder

It is possible to create a logical circuit using multiple full adders to add N-bit numbers. Each full adder inputs a Cin, which is the Cout of the previous adder. This kind of adder is a ripple carry adder, since each carry bit "ripples" to the next full adder. Note that the first (and only the first) full adder may be replaced by a half adder.

The layout of ripple carry adder is simple, which allows for fast design time; however, the ripple carry adder is relatively slow, since each full adder must wait for the carry bit to be calculated from the previous full adder. The gate delay can easily be calculated by inspection of the full adder circuit. Each full adder requires three levels of logic. In a 32-bit [ripple carry] adder, there are 32 full adders, so the critical path (worst case) delay is 31 * 2(for carry propagation) + 3(for sum) = 65 gate delays.

Carry look-ahead adders

Main article: Carry look-ahead adder

To reduce the computation time, engineers devised faster ways to add two binary numbers by using carry lookahead adders. They work by creating two signals (P and G) for each bit position, based on whether a carry is propagated through from a less significant bit position (at least one input is a '1'), a carry is generated in that bit position (both inputs are '1'), or if a carry is killed in that bit position (both inputs are '0'). In most cases, P is simply the sum output of a half-adder and G is the carry output of the same adder. After P and G are generated the carries for every bit position are created. Some advanced carry look ahead architectures are the Manchester carry chain, Brent-Kung adder, and the Kogge-Stone adder.

Some other multi-bit adder architectures break the adder into blocks. It is possible to vary the length of these blocks based on thepropagation delay of the circuits to optimize computation time. These block based adders include the carry bypass adder which will determine P and G values for each block rather than each bit, and the carry select adder which pre-generates sum and carry values for either possible carry input to the block.

Other adder designs include the conditional sum adder, carry skip adder, and carry complete adder.

Lookahead Carry Unit

Main article: Lookahead Carry Unit

By combining multiple carry look-ahead adders even larger adders can be created. This can be used at multiple levels to make even larger adders. For example, the following adder is a 64-bit adder that uses four 16-bit CLAs with two levels of LCUs.

3:2 compressors

We can view a full adder as a 3:2 compressor: it sums three one-bit inputs, and returns the result as a single two-bit number. Thus, for example, an input of 101 results in an output of 1+0+1=10 (2). The carry-out represents bit one of the result, while the sum represents bit zero. Likewise, a half adder can be used as a 2:2 compressor.

3:2 compressors can be used to speed up the summation of three or more addends. If the addends are exactly three, the layout is known as the carry-save adder. If the addends are four or more, more than one layer of compressors is necessary and there are various possible design for the circuit: the most common are Dadda and Wallace trees. This kind of circuit is most notably used in multipliers, which is why these circuits are also known as Dadda and Wallace multipliers.

No comments:

Post a Comment