In digital logic and computing, a counter is a device which stores (and sometimes displays) the number of times a particular event or process has occurred, often in relationship to a clock signal. In practice, there are two types of counters:

- Up counters, which increase (increment) in value

- Down counters, which decrease (decrement) in value

In electronics

In electronics, counters can be implemented quite easily using register-type circuits such as the flip-flop, and a wide variety of designs exist, e.g.:

- Asynchronous (ripple) counter – changing state bits are used as clocks to subsequent state flip-flops

- Synchronous counter – all state bits change under control of a single clock

- Decade counter – counts through ten states per stage

- Up–down counter – counts both up and down, under command of a control input

- Ring counter – formed by a shift register with feedback connection in a ring

- Johnson counter – a twisted ring counter

- Cascaded counter

Each is useful for different applications. Usually, counter circuits are digital in nature, and count in natural binary. Many types of counter circuit are available as digital building blocks, for example a number of chips in the 4000 series implement different counters.

Occasionally there are advantages to using a counting sequence other than the natural binary sequence—such as the binary coded decimalcounter, a linear feedback shift register counter, or a Gray-code counter.

Counters are useful for digital clocks and timers, and in oven timers, VCR clocks, etc.

Asynchronous (ripple) counter

An asynchronous (ripple) counter is a single D-type flip-flop, with its D (data) input fed from its own inverted output. This circuit can store one bit, and hence can count from zero to one before it overflows (starts over from 0). This counter will increment once for every clock cycle and takes two clock cycles to overflow, so every cycle it will alternate between a transition from 0 to 1 and a transition from 1 to 0. Notice that this creates a new clock with a 50% duty cycle at exactly half the frequency of the input clock. If this output is then used as the clock signal for a similarly arranged D flip-flop (remembering to invert the output to the input), you will get another 1 bit counter that counts half as fast. Putting them together yields a two bit counter:

Cycle | Q1 | Q0 | (Q1:Q0)dec |

|---|---|---|---|

0 | 0 | 0 | 0 |

1 | 0 | 1 | 1 |

2 | 1 | 0 | 2 |

3 | 1 | 1 | 3 |

4 | 0 | 0 | 0 |

You can continue to add additional flip-flops, always inverting the output to its own input, and using the output from the previous flip-flop as the clock signal. The result is called a ripple counter, which can count to 2n-1 where n is the number of bits (flip-flop stages) in the counter. Ripple counters suffer from unstable outputs as the overflows "ripple" from stage to stage, but they do find frequent application as dividers for clock signals, where the instantaneous count is unimportant, but the division ratio overall is. (To clarify this, a 1-bit counter is exactly equivalent to a divide by two circuit; the output frequency is exactly half that of the input when fed with a regular train of clock pulses).

The use of flip-flop outputs as clocks leads to timing skew between the count data bits, making this ripple technique incompatible with normalsynchronous circuit design styles.

Synchronous counter

A simple way of implementing the logic for each bit of an ascending counter (which is what is depicted in the image to the right) is for each bit to toggle when all of the less significant bits are at a logic high state. For example, bit 1 toggles when bit 0 is logic high; bit 2 toggles when both bit 1 and bit 0 are logic high; bit 3 toggles when bit 2, bit 1 and bit 0 are all high; and so on.

Synchronous counters can also be implemented with hardwarefinite state machines, which are more complex but allow for smoother, more stable transitions.

Hardware based counters are of this type.

Ring counter

A ring counter is a shift register (a cascade connection of flip-flops) with the output of the last one connected to the input of the first, that is, in a ring. Typically a pattern consisting of a single 1 bit is circulated, so the state repeats every N clock cycles if N flip-flops are used. It can be used as a cycle counter of N states.

Johnson counter

A Johnson counter (or switchtail ring counter, twisted-ring counter, walking-ring counter, or Moebius counter) is a modified ring counter, where the output from the last stage is inverted and fed back as input to the first stage. A pattern of bits equal in length to twice the length of the shift register thus circulates indefinitely. These counters find specialist applications, including those similar to the decade counter, digital to analog conversion, etc.

Decade counter

A decade counter is one that counts in decimal digits, rather than binary. A decimal counter may have each digit binary encoded (that is, it may count in binary-coded decimal, as the 7490 integrated circuit did) or other binary encodings (such as the bi-quinary encoding of the 7490integrated circuit). Alternatively, it may have a "fully decoded" or one-hot output code in which each output goes high in turn; the 4017 was such a circuit. The latter type of circuit finds applications in multiplexers and demultiplexers, or wherever a scanning type of behavior is useful. Similar counters with different numbers of outputs are also common.

The decade counter is also known as a mod-counter.

Up–down counter

A counter that can change state in either direction, under control an up–down selector input, is known as an up–down counter. When the selector is in the up state, the counter increments its value; when the selector is in the down state, the counter decrements the count.

In computer science

In computability theory, a counter is considered a type of memory. A counter stores a single natural number (initially zero) and can be arbitrarily many digits long. A counter is usually considered in conjunction with a finite-state machine (FSM), which can perform the following operations on the counter:

- Check whether the counter is zero

- Increment the counter by one

- Decrement the counter by one (if it's already zero, this leaves it unchanged).

The following machines are listed in order of power, with each one being strictly more powerful than the one below it:

- Deterministic or non-deterministic FSM plus two counters

- Non-deterministic FSM plus one stack

- Non-deterministic FSM plus one counter

- Deterministic FSM plus one counter

- Deterministic or non-deterministic FSM

For the first and last, it doesn't matter whether the FSM is a deterministic finite-state machine or a nondeterministic finite-state machine. They have equivalent power. The first two and the last one are levels of the Chomsky hierarchy.

The first machine, an FSM plus two counters, is equivalent in power to a Turing machine. See the article on register machines for a proof.

Mechanical counters

Long before electronics became common, mechanical devices were used to count events. These typically consist of a series of disks mounted on an axle, with the digits 0 through 9 marked on their edge. The right most disk moves one increment with each event. Each disk except the left-most has a protrusion that, after the completion of one revolution, moves the next disk to the left one increment. Such counters were originally used to control manufacturing processes, but were later used as odometers for bicycles and cars and in fuel dispensers. One of the largest manufacturers was the Veeder-Root company, and their name was often used for this type of counter.

.jpg)

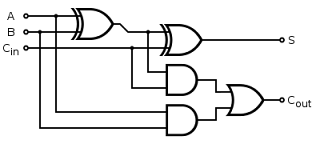

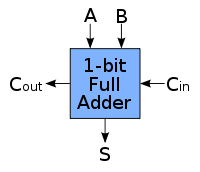

. Following is the logic table for a half adder:

. Following is the logic table for a half adder:

| Adder |

| |-----

| Adder |

| |-----  B ------|___________|

B ------|___________|

and

and  .

.